Processor addressable memory regions

What are processor addressable memory locations?

Consider Figure 1. Here, there is a system bus(AHB) that connects the processor with the peripherals and with the memory.

In ARM Cortex Mx based microcontroller, this is a central bus which connects peripherals, processor, and memories. And this bus is also called a system bus, which is based on the AHB specification designed by ARM, and AHB stands for Advanced High-performance Bus, so that’s a specification.

This bus comprises 2 channels.

- 32 bit address channel

- 32 bit data channel

It means that a System bus has a 32-bit address bus. That means you can put 2 to the power 32 a different address on this bus in order to target different peripherals and different memories.

For example, you want to transmit data from Data memory to the GPIOD peripheral, and you have to send that data out to the external world over the ports of the GPIOD peripheral. So, if this is your objective, then you have to send the data over this system bus and send that data to one of the registers of this GPIOD peripheral. And if you place the data into that register of this GPIOD peripheral, the data will be transmitted to the IO pins to the external world. That’s how it works.

Peripherals are controlled by their own set of registers, and a register is addressed by its unique address.

That means that you have to find out which address you have to place on this address bus to target this particular peripheral so that you have to find out.

Now, we know the details by going through the memory map of the processor. You cannot put any random address on the address bus to target a peripheral.

For example, in this case, if you want to target ADC peripheral, let’s say you want to read the data from the ADC into the memory. So, you have to place the appropriate address on the address bus to read data from the data register of the ADC peripherals.

This AHB system bus, as I said, comprises an address channel whose width is 32-bit. That means you can put 2 to the power 32 different memory locations. That is 4 gig. 4 gig different memory location values onto the address bus in order to target different peripherals and different memories. The processor can produce 4 gig of different memory locations on the address bus to target different memories and peripherals.

Conclusion

Now, let’s conclude processor addressable memory location.

Since the address bus width is 32 bits, processor can put address ranging from 0x0000_0000 to 0xFFFF_FFFF on the address bus.

That means 4G(4, 29, 49, 67, 296) different addresses can be put on the address bus.

Now let’s understand how these different addresses are arranged to address, different memories and different peripherals of the microcontroller.

When the processor puts these memory locations on the address bus, the address bus will be targeting to the code memory of the microcontroller.

When the processor puts, the processor means the address generation unit of the processor, so there is an address generation unit inside the processor that will get activated when an instruction is decoded.

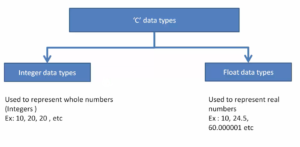

So, when I say processor, that means the address generation unit of the processor. When the processor puts an address which belongs to this region on the address bus, then the address bus will be talking to the data in the memory of the microcontroller. Similarly, when the processor puts an address on the address bus, which falls in this region, then the address bus will be talking to the peripherals of the microcontroller like that. So this arrangement is called as Memory map of the processor. This is fixed. This is fixed by the ARM Cortex Mx architecture, and the microcontroller designers who use ARM Cortex Mx processors in their design should follow this memory map.

The above diagram(Figure 2) is also mentioned in the ARM Cortex Mx technical reference manual so that you can explore it from the document.

To conclude this memory map of the processor, remember that program memory, data memory, registers of various peripherals are organized within the same linear 4G byte of address space.

So, GPIOD is our peripheral. The addresses of GPIOD registers must fall within this address (0x40000000 to 0x60000000).

In later articles, we’ll find out the exact address of the GPIOD registers. So, when you have 0x40000000 of this address at your hand, then your job becomes very easy. You already know the pointers. So, treat this as a pointer, and you can start writing and reading data from this pointer. That’s how you control the peripheral.

Now let’s do one thing: Explore the real memory map of the STM32 microcontroller. You can refer to the microcontroller’s memory map from the datasheet or reference manual of the microcontroller. I will take up this in the following article.

FastBit Embedded Brain Academy Courses

Click here: https://fastbitlab.com/course1