Bus Protocols and Bus interfaces of Cortex M3/M4 Processor

In this Article, let’s explore about the Bus protocols and bus interfaces used in the Cortex m3 /m4 processor based MCUs.

There are 2 bus protocols, which are very famous for interconnection between processor and the various Peripheral of the microcontroller.

1) The AHB Lite

2) APB

The AHB Lite

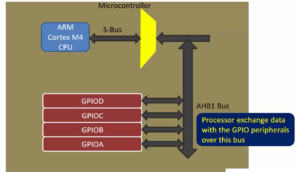

The Cortex M3/M4 processor use AHB lite as the main system bus.

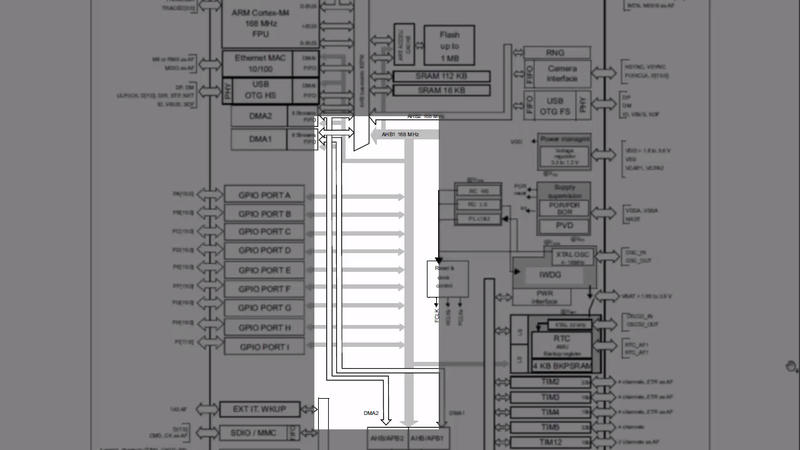

As you can see in this figure.

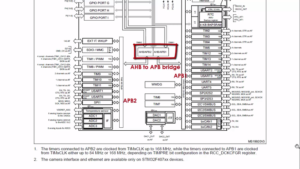

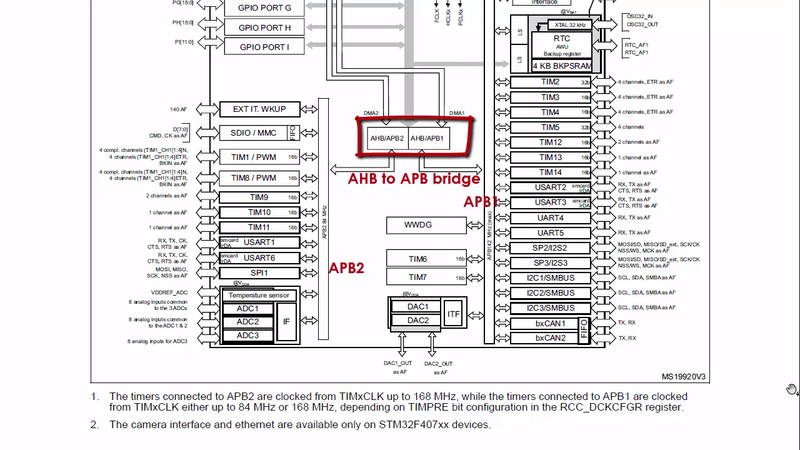

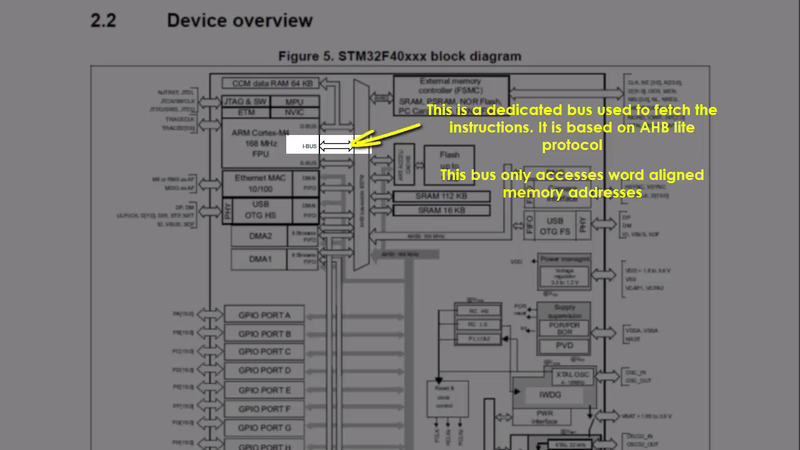

This is figure shows, what are the bus interfaces exist inside the ST microcontroller and how the peripherals are hooked up to different buses.

The AHB lite stands for advanced high performance bus which is actually a lighter version of AMBA bus specification. The AMBA, which stands for Advanced Microcontroller Bus Architecture is the de – facto standard for on chip interconnections with the processor.

APB

Then the next important bus protocol is APB, Which stands for Advanced Peripheral Bus.

The APB bus also derived from AMBA specification, but this is optimized for minimum power and reduced interface complexity. So basically, it is much simpler then the AHB lite. It’s mainly used to connect peripherals like UART, timers , serial protocols like SPI, I2C etc.., which do not need the high performance like AHB lite.

Here you can see various peripherals are hooked up to APB1 and APB2 bus interfaces.

There is a bridge which convert AHB lite protocol to APB protocol.

The cortex m3/m4 provides 3 external AHB lite bus interface of 32 bit.

The first one is called I-code interface, which is a 32 bit AHB lite bus interface.

This is delicately used for instruction fetches and vector table fetches from the code memory region.

All fetches on this bus are word aligned.

So, in the case of 16 bit instruction, 2 instruction are fetched at a time.

Since, all thumb instructions are half word aligned in memory, two thumb instructions are fetched at a time.

The D code interface is also based on AHB lite protocol and this is a dedicated bus which connects to the code memory for data accesses.

Interesting thing about this interface is, it supports unaligned data accesses. It means, to access data over this bus, the data bytes need not to be aligned in the memory.

Next we have system bus which is also 32 bit AHB lite bus. This bus also allows instruction fetch and data accesses from the memory devices such as SRAM.

Various peripherals like SRAM , bus masters like USB, DMA, and high speed peripherals are connected over this bus.

To connect slower peripherals need not to use AHB lite bus,

What they do is , they convert the AHB bus logic to APB bus logic using an AHB to APB bridge as shown in the above image.

Using APB bus for peripherals which doesn’t demand high performance of AHB bus can save a lot of power in the microcontroller design.

So, in the typical microcontroller you will see there are 2 or more APB buses coming out of a bridge to connect various peripherals.

Great! hope you understood about the bus interfaces of the the typical microcontroller.

Please, comment below if you have any questions and please consider sharing this in your linkedin profile.

Watch this video which explains in detail.

FastBit Embedded Brain Academy Courses,

Click here: https://fastbitlab.com/course1