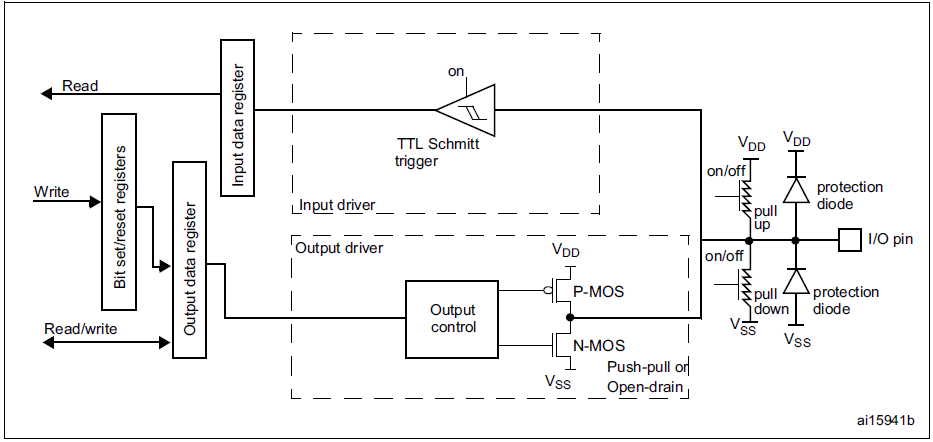

Output configuration of GPIO Pin in Open drain mode

In Open-drain configuration, PMOS doesn’t exist, and two output possibilities are high or floating.

A “0” in the Output data register activates the N-MOS and the I/O pin driven to the ground.

Whereas “1” in the Output data register leaves the port in Hi-Z (the P-MOS is never activated), so I/O state is not defined.

To solve this issue either activate internal pull-up resistor or give an external pull-up resistor. So, once a pull-up resistor is activated, the I/O pin gets its state to VDD. To set GPIO output type register in open-drain mode, in GPIO_OTYPER register bit is set to “1”.

In the following article, let’s see Alternate functionality configuration of a GPIO pin.

FastBit Embedded Brain Academy Courses,

Click here: https://fastbitlab.com/course1