Setting up main system clock code implementation part-2

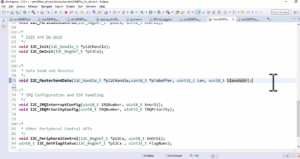

The process of setting up the PLL_M, PLL_N, and PLL_P codes is depicted below.

void SystemClock_Setup(void) { RCC_TypeDef *pRCC = RCC; // Setting up main PLL REG_SET_VAL(pRCC->PLLCFGR,0x8U,0x3FU,0U); /*PLL_M*/ REG_SET_VAL(pRCC->PLLCFGR,180U,0x1FFU,6U); /*PLL_N*/ REG_SET_VAL(pRCC->PLLCFGR,0x00U,0x3U,16U); /*PLL_P*/

To elaborate on this process, line 45 utilizes the value of 180 for PLL_N and a mask value of 1FF. It is important to note that the position for PLL_N begins at 6. For PLL_P, the value is set to 0, as opposed to 2.

According to the reference manual, if PLLP is 0 and the bit positions are also 0, then it’s equal to 2.

Using RCC block, you can utilize the macros given by the device header file, as shown in below(Instead of bit positions use macros). This includes the use of RCC_PLLCFGR_PLLM_Pos for M, RCC_PLLCFGR_PLLN_pos for N, and RCC_PLLCFGR_PLLP_Pos for P.

void SystemClock_Setup(void) { RCC_TypeDef *pRCC = RCC; // Setting up main PLL REG_SET_VAL(pRCC->PLLCFGR,0x8U,0x3FU,RCC_PLLCFGR_PLLM_Pos); /*PLL_M*/ REG_SET_VAL(pRCC->PLLCFGR,180U,0x1FFU,RCC_PLLCFGR_PLLN_Pos); /*PLL_N*/ REG_SET_VAL(pRCC->PLLCFGR,0x00U,0x3U,RCC_PLLCFGR_PLLP_Pos); /*PLL_P*/

Our next task is to focus on the clock tree. While we have configured the values for M, P, and N, it is important to note that our system clock is not necessarily set to 180 megahertz. To turn on this PLL, we will need to perform this step later.

It is important to note that the PLL engine creates our DOTCLK at a frequency of 6MHz for this task.

We must determine the necessary DOTCLK frequency that the display module requires; this is dependent on the display module’s capability. A high-speed DOTCLK may cause the display module to fail to interpret such a high-frequency clock.

To determine the necessary DOTCLK frequency, we can consult the datasheet of the ILI9341, which provides information on clock frequencies on page 46, assuming a clock frequency of 6.35MHz (as shown in Figure 5).

We should use the pixel clock of 6 to 7MHz for this controller.

Additionally, if we are using this driver chip, OTA5180A, which is being used in STM32F7 Discovery Board.

Here, in this table(Figure 7), you can see that the maximum value for DCLK frequency is 12MHz.

When it comes to PLLSAI, we must refer to the RCC PLL configuration register, as shown in Figure 8, to configure R and N.

Furthermore, we can use RCC Dedicated Clock Configuration Register (Figure 9) for the divider, with its value must be between 2 to 16 to control the frequency of LCD_CLK.

Get the Full Course on STM32-LTDC, LCD-TFT, LVGL (MCU3) Here.

FastBit Embedded Brain Academy Courses

Click here: https://fastbitlab.com/course1