Setting up main system clock code implementation part-4

Setup main system clock(SYSCLK)

- Configure main PLL parameters

- Configure PLLSAI parameters

- Configure AHB, APBx prescalers

- Turn on the main PLL

- Wait until PLLCLK ready bit is set

- Switch PLLCLK as SYSCLK

- Wait for switch status

- Configure FLASH wait states:

- To correctly read data from Flash memory, the number of wait states(LATENCY) must be correctly programmed in the Flash access control register(FLASH_ACR) according to the frequency of the CPU clock(HCLK) and the supply voltage of the device.

- Turn on PLLSAI

- Wait until PLLSAICLK ready bit is set

We completed the above three steps in the previous article. The next step is to Turn on the main PLL. Once you have turned on the PLL, you need to wait until the PLL clock is generated, which can take some time. You should wait until the PLLCLK ready bit is set, indicating that the PLLCLK is ready.

Once the PLLCLK bit is set, that means the PLL clock is ready and you have to switch PLLCLK as SYSCLK, that is the main system clock.

Next, you should wait for the switch status. It may take some time for the microcontroller to make the switch. After that, you need to perform one more important step here.

Since you have increased the HCLK, the Flash memory may not respond to such a high frequency. The Flash read may fail or the bus may return an error or something like that.

That’s why, what this reference manual says is, to correctly read data from Flash memory, the number of wait states(LATENCY) must be correctly programmed in the Flash access control register(FLASH_ACR) according to the frequency of the CPU clock(HCLK) and the supply voltage of the device.

You can find this table in the reference manual under the section “Embedded Flash Memory”. From this table, you can see that our voltage range falls between 2.7V – 3.6V and our HCLK falls between 150<HCLK≤180. Therefore, you need to program 6 CPU cycles of latency into the flash control register. This means you have to program the value 5 into the FLASH_ACR register.

After that, you may turn on the PLLSAI because we need the LCD_CLK to be active. Wait until the PLLSAICLK is ready.

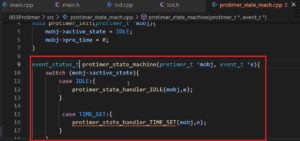

Let me now show you the place where you can carry out these steps.

RCC clock control register, as shown in Figure 2.

Here, you will find the PLLON bit that you can toggle to turn on the PLL. Additionally, you will find the PLLRDY bit that you should wait for to be set before proceeding. Similarly, to turn on the PLLSAI block, use the PLLSAI ON bit, and wait for the PLLSAI RDY bit to be set. This will indicate that the clock is ready.

Once the PLLRDY bit is set, you need to switch to another bit. Where can you find the switch bit? Let’s navigate to the RCC clock configuration register. You can find the switch (SW) there.

You have to use two-bit fields, namely SW and SWS.

Therefore, you have to set SW switch to 10(one zero). That means, PLL selected as system clock. Once you do that, you have to wait until the System clock switch status is updated by the microcontroller.

You can see that, it is set and cleared by the hardware. So, the software cannot modify these bits. It is read-only. Hardware updates these fields.

So, if this bit field gives you the value 2, that is one zero(10), which means, PLL used as the system clock.

How do you access the flash registers?

For that, you have to get the base address from where the registers of the Flash start in the memory map of the microcontroller. For that, you have to use the flash register definition structure.

FLASH_TypeDef *pFlash = FLASH;

Get the Full Course on STM32-LTDC, LCD-TFT, LVGL (MCU3) Here.

FastBit Embedded Brain Academy Courses

Click here: https://fastbitlab.com/course1