I2C IRQ handler implementation Part 2

Steps to implement interrupt handling for SB event:

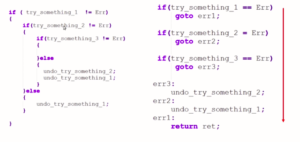

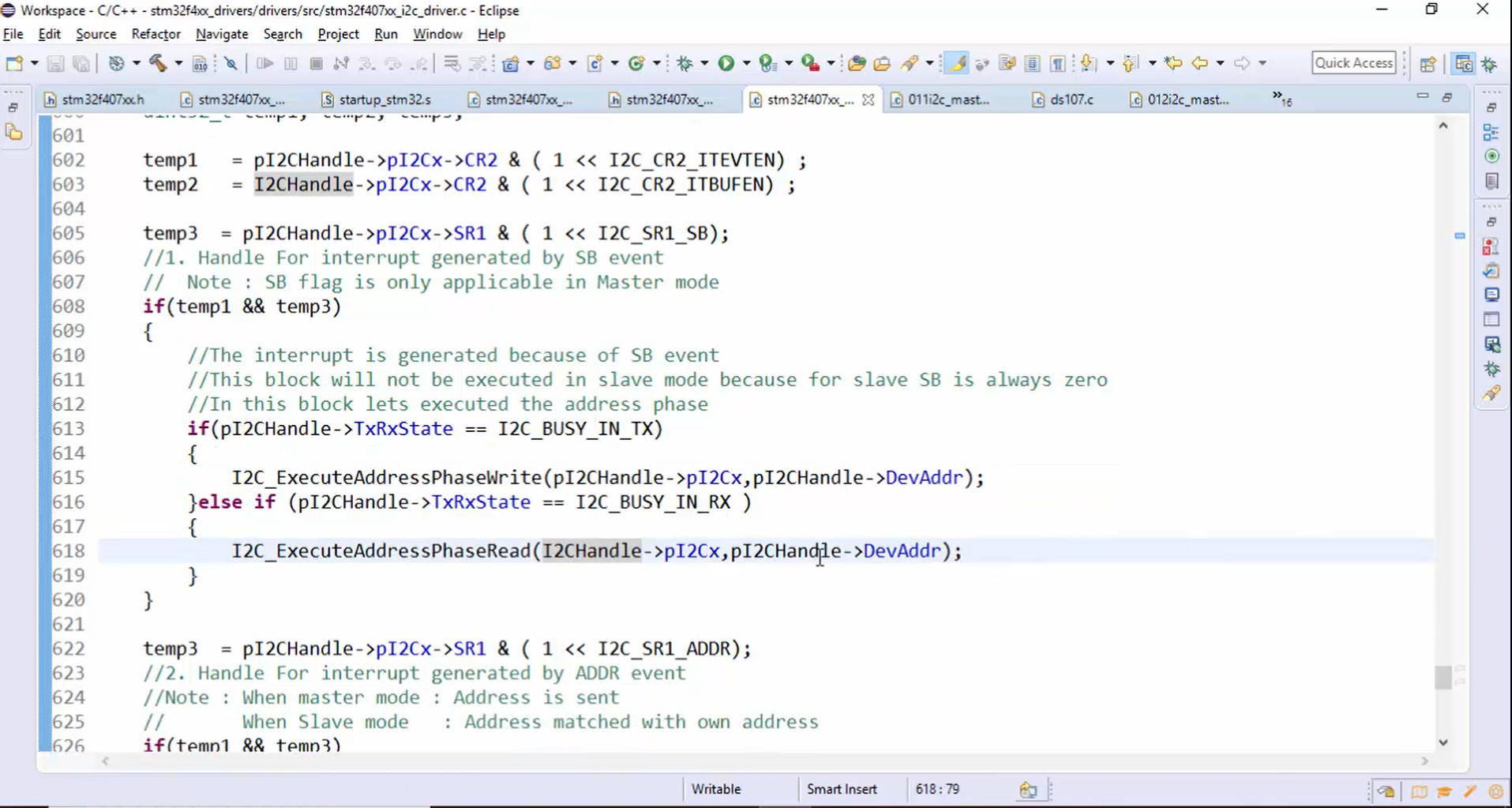

- If the control enters into the if block, shown in Figure 1, the interrupt is generated because of the SB event. Remember that it is mentioned in the reference manual that this if block will not be executed in slave mode because for the slave, the flag SB is always 0.

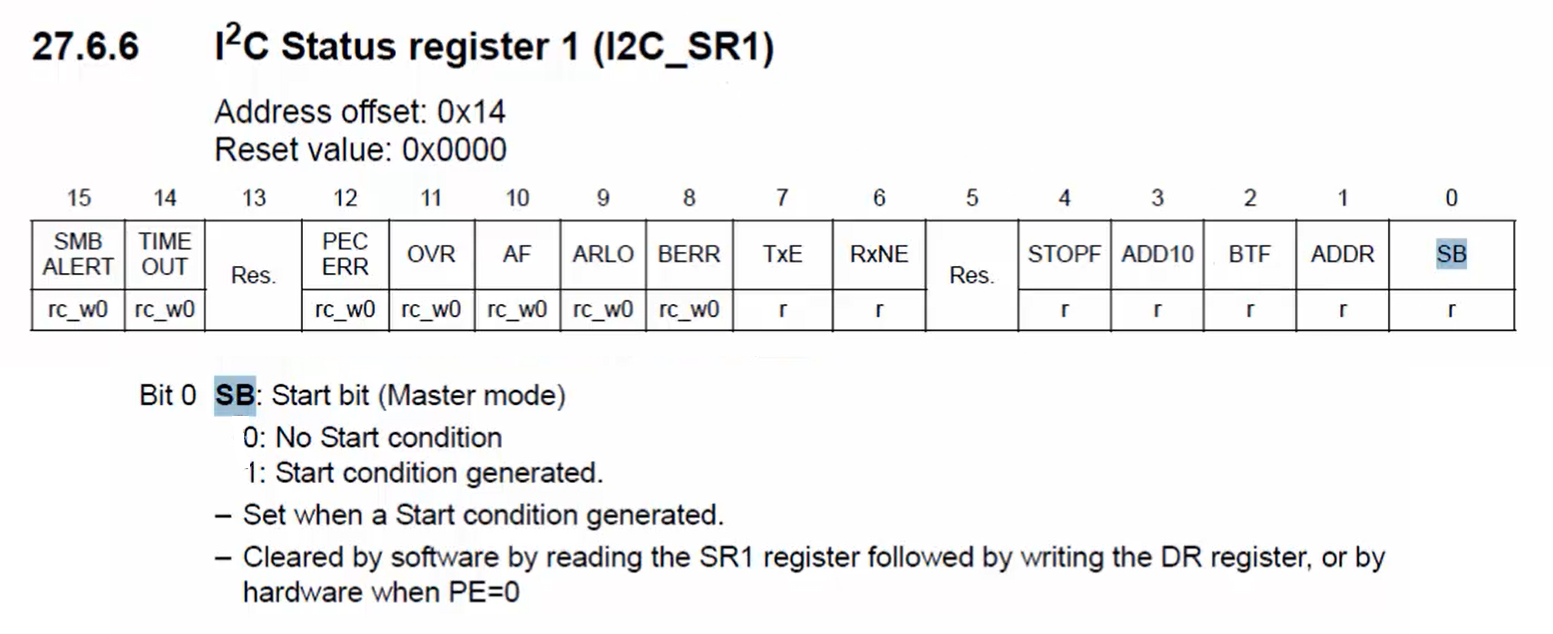

- Go to the SR1 register of the reference manual and check the SB bit (Figure 2). Here it is written that the SB flag is applicable only in the master mode. If this flag is set, that means the start condition is generated. The SB bit is cleared by reading the SR1 and followed by writing to the DR register. That means when control reaches the if block shown in Figure 1, it guarantees that the SB generation was successful and completed.

- Once the start is generated, the next step is to perform the address phase. Therefore, perform the address phase within the if block, as shown in Figure 3. There are two APIs for executing the address phase, one is I2C_ExecuteAddressPhaseRead() and another is I2C_ExecuteAddressPhaseWrite(). Depending on the state of the I2C application, you have to select either of two APIs.

- If the I2C application’s state is busy in transmission (TX), then call I2C_ExecuteAddressPhaseWrite() API.

- If the I2C application’s state is busy in RX, then call I2C_ExecuteAddressPhaseRead() API.

Therefore, to perform the address phase, first, you have to check the TXRX state in the handle and then take the decision according to the value, as shown in Figure 3.

Flow of control:

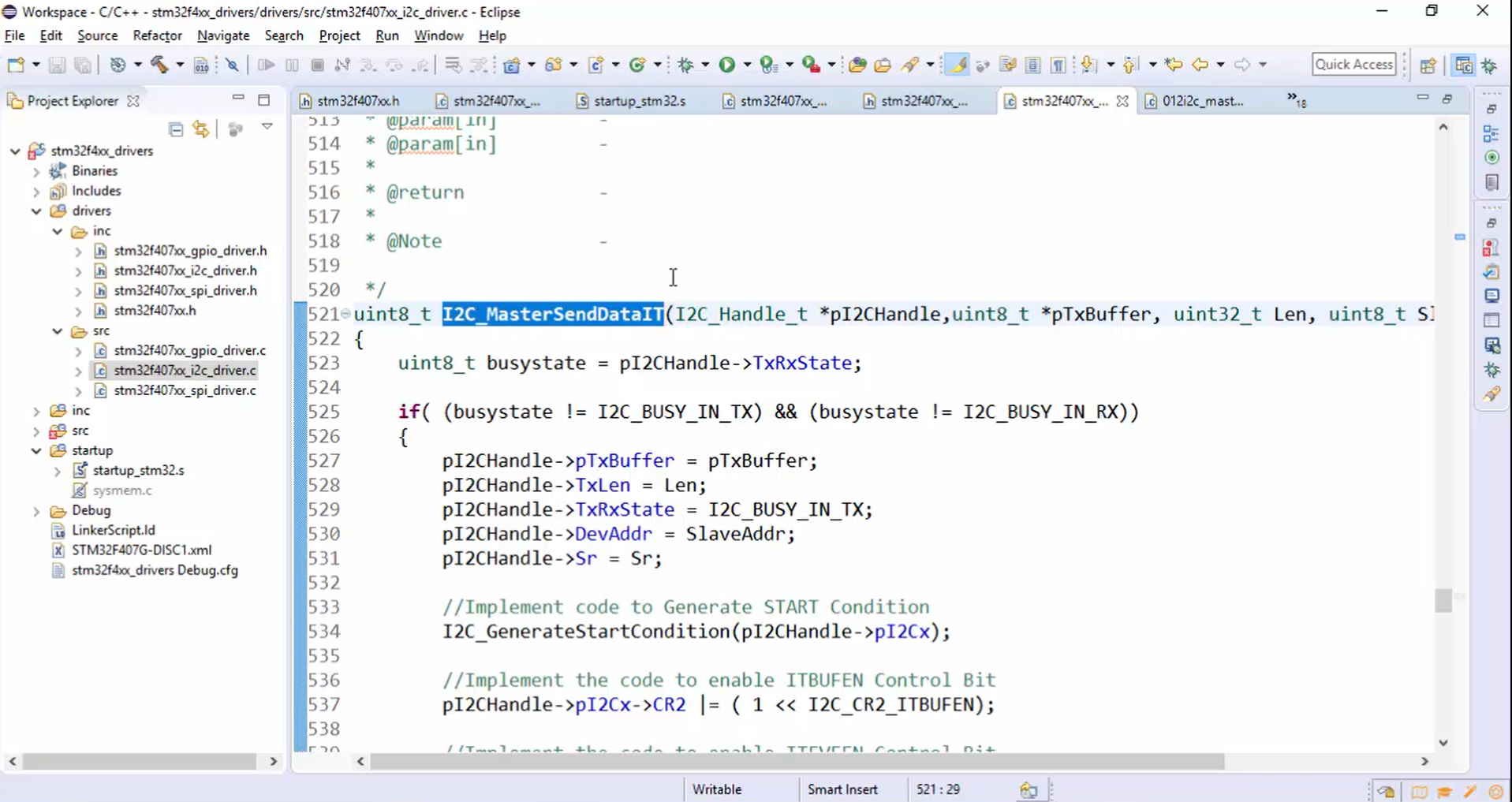

- Suppose the user application wants to transmit the data using interrupt mode. In that case, the application uses MasterSendDataIT API shown in Figure 4, in which the start condition is triggered, and all the control bits are enabled to generate the interrupt.

- Once the start generation is successful, the SB flag will be set, and an interrupt will be generated. Once the interrupt is generated, the control comes to the event IRQ handling (I2C_EV_IRQHandling), where the state of the SB flag is verified, and the address phase is performed if the SB bit is set. The API for executing the address phase is decided based on the I2C application’s state.